Elaborado por Erick Carvajal Barboza

Email: erick punto carvajal punto barboza arroba ucr punto ac punto cr

Escuela de Ingeniería Eléctrica, Universidad de Costa Rica

Para encontrar una lista actualizada de las preguntas más comunes puede ir al siguiente enlace.

Los sistemas digitales pueden ser descritos en varios dominios distintos (Kaeslin, 2008), de más a menos abstracto se tiene: (1) el dominio conductual, (2) el dominio estructural y (3) el dominio físico.

En el dominio conductual únicamente es importante la funcionalidad del sistema, y no tiene relevancia el cómo está construido. En el dominio estructural se especifican las interconexiones de cada bloque que conforma el sistema sin embargo, es únicamente en el dominio físico en el cuál se tiene información sobre cómo está construido cada componente, que ubicación tiene en el chip y cómo se deben realizar las conexiones entre bloques. El flujo de diseño de circuitos integrados se encarga de convertir la especificación conductual de un sistema digital en una especificación física, y para eso tiene, como paso intermedio, que obtener une especificación estructural.

El paso que permite la conversión de una especificación conductual de un sistema digital a una especificación estructural se conoce como síntesis lógica (Weste & Harris, 2015) y fue estudiado ampliamente en el tutorial anterior. El presente tutorial se enfoca en el paso que se encarga de convertir la especificación estructural a una especificación física, el cual se conoce como diseño físico (Weste & Harris, 2015).

Asegúrese de haber completado todos los experimentos del primer tutorial,

en particular el sumador de 4 bits, y el sumador de 8 bits con pipeline. Es

indispensable que ya haya agregado ambos diseños al flujo de OpenLane

(mediante el la ejecución del archivo flow.tcl con las banderas

-init_design_config y -add_to_designs, lo cual fue

realizado en el tutorial anterior).

En esta sección se ejecutará el flujo de diseño de OpenLane para el sumador de 4 bits utilizado en el tutorial anterior.

Para este paso, utilice como inicial

Para ejecutar el flujo de OpenLane, abra el Docker de OpenLane y ejecute el siguiente comando:

:/openlane$ ./flow.tcl -design adder_4b -tag

Durante la ejecución de este comando el flujo fallará. Revise todos los

WARNING y ERROR mostrados por OpenLane. ¿Cuál es el

problema que impide que la ejecución del flujo se complete satisfactoriamente?

Usando la herramienta Magic se puede observar el resultado

intermedio que se tenía hasta el momento en el que falló la corrida. Para esto,

utilice el comando mostrado a continuación :

:/openlane$ magic -T pdks/sky130A/libs.tech/magic/sky130A.tech lef read designs/adder_4b/runs//tmp/merged.nom.lef def read designs/adder_4b/runs//results//adder_4b.def

Deberá sustituir

Para solucionar el problema del apartado anterior, se deberá modificiar el

archivo de configuración config.json que se encuentra en la

carpeta designs/adder_4b/. Ingrese las siguientes configuraciones

en su archivo.

{

"DESIGN_NAME": "adder_4b",

"VERILOG_FILES": "dir::src/*.v",

"CLOCK_PORT": null,

"CLOCK_PERIOD": 10.0,

"DESIGN_IS_CORE": true,

"FP_PDN_AUTO_ADJUST": false,

"FP_PDN_VPITCH": 20,

"FP_PDN_HPITCH": 20,

"FP_PDN_VOFFSET": 0,

"FP_PDN_HOFFSET": 0,

"FP_SIZING": "absolute",

"DIE_AREA": "0 0 35 60"

}

Investigue en la documentación de OpenLane sobre el significado de cada una de las opciones que se están configurando.

Ahora, utilizando como area_pdn_config, vuelva a intentar ejecutar el flujo de diseño

de OpenLane, utilizando el comando brindado en la sección anterior. En esta

ocasión, el flujo debería completarse satisfactoriamente.

Note que durante la ejecución del flujo, se ejecutan una serie de pasos, los cuales aparecen enumerados en la terminal. Investigue sobre los siguientes pasos del flujo de diseño de circuitos integrados:

Utilizando la herramienta Magic, abra el layout final obtenido por

OpenLane. La dirección del archivo lef se mantiene idéntica a la

utilizada anteriormente, mientras que el def será:

designs/adder_4b/runs/.

Analice el layout obtenido.

config.json, pero en esta

ocasión cambie el FP_PDN_HPITCH a 10. Abra el nuevo layout

y compárelo con el layout obtenido cuando FP_PDN_HPITCH era 20.

Explique ¿Cómo afectó este cambio el resultado final del layout?

FP_PDN_HPITCH en 10, modifique la variable de

configuración DIE_AREA para que, manteniendo un lado de 60

y otro de 35, el circuito ahora sea más alto que ancho.

Abra el layout, y compárelo con los layouts obtenidos anteriormente.

Explique ¿Cómo afectó este cambio el resultado final del layout?

En esta sección se ejecutará el flujo de diseño de OpenLane para el sumador de 8 bits con pipeline utilizado en el tutorial anterior.

Para este paso, utilice como inicial.

Utilice la siguiente configuración en su archivo config.json:

{

"DESIGN_NAME": "adder_8b_pipeline",

"VERILOG_FILES": "dir::src/*.v",

"CLOCK_PORT": "clk",

"CLOCK_PERIOD": 10.0,

"DESIGN_IS_CORE": true,

"FP_SIZING": "absolute",

"DIE_AREA": "0 0 30 50",

"FP_PDN_AUTO_ADJUST": false,

"FP_PDN_VPITCH": 20,

"FP_PDN_HPITCH": 20,

"FP_PDN_VOFFSET": 0,

"FP_PDN_HOFFSET": 0

}

Para ejecutar el flujo de OpenLane, abra el Docker de OpenLane y ejecute el siguiente comando:

:/openlane$ ./flow.tcl -design adder_8b_pipeline -tag

Durante la ejecución de este comando el flujo fallará. Revise todos los

WARNING y ERROR mostrados por OpenLane.

¿Cuál es el problema que impide que la ejecución del flujo se complete

satisfactoriamente?

Utilizando el parámetro de configuración DIE_AREA cambie el

ANCHO del chip. Encuentre una dimensión que permita que el flujo se ejecute

correctamente, manteniendo el área lo más pequeña posible.

Abra el layout.

Utilizando la corrida anterior, determine si existe algún path

que produzca una violación de timing. Para esto, revise los

logs y reports de la etapa signoff del flujo.

Analice el reporte de temporización de las trayectorias críticas (las que

tengan el slack más pequeño) para el análisis de

setup y de hold.

Ahora, modifique el archivo \texttt{config.json} para que el período del reloj sea 4.0 y vuelva a correr el flujo de diseño.

Revise los resultados de temporización para el diseño con la nueva frecuencia de reloj, tanto los de Single-Corner STA como los de Multi-Corner STA. ¿Se cumplen los requerimientos de temporización (tanto para análisis máximo como mínimo) en este caso? ¿Es el peor path el mismo (inicio y final) en ambos períodos de reloj? ¿Sufrió cambios la lógica del path ante el cambio en la frecuencia?

Abra en Magic el layout generado para el sumador de 8 bits con

pipeline en la sección anterior. Observe el orden y la posición en la que

fueron ubicados los puertos de entradas y salidas al diseño

(A[0-7], B[0-7], C\_in, Sum[0-7], C\_out, clk y rst). Dibuje

un diagrama donde indique la posición de los puertos en el diseño.

¿Considera usted que el ordenamiento actual es el ideal? ¿Por qué?

Agregue un diagrama con un ordenamiento que usted considere podría

mejorar los resultados.

Abra en Magic el layout generado para el sumador de 8 bits con

pipeline en la sección anterior. Observe el orden y la posición en la que

fueron ubicados los puertos de entradas y salidas al diseño

(A[0-7], B[0-7], C\_in, Sum[0-7], C\_out, clk y rst). Dibuje

un diagrama donde indique la posición de los puertos en el diseño.

¿Considera usted que el ordenamiento actual es el ideal? ¿Por qué?

Realice un diagrama con un ordenamiento que usted considere podría

mejorar los resultados.

Ahora, se procederá a implementar el ordenamiento que usted propuso en

el diseño. Para esto debe crear un archivo llamado pin_order.cfg

en el directorio del diseño (designs/adder_8b_pipeline/)

e indicarle a OpenLane que el archivo nuevo es el que debe utilizarse.

Para eso declare la variable FP_PIN_ORDER_CFG en el archivo

config.json y use "dir::pin\_order.cfg" como valor.

El archivo pin_order.cfg define el ordenamiento que se utilizará

para colocar los puertos en cada lado del chip. Para esto se indicara uno

de los costados #N, #W, #S, #E (North, West, South, East),

seguido de los puertos que desean colocar. Los puertos se colocarán según el

orden dado y de izquierda a derecha (para #N y #S)

o de abajo hacia arriba (para #W y #E).

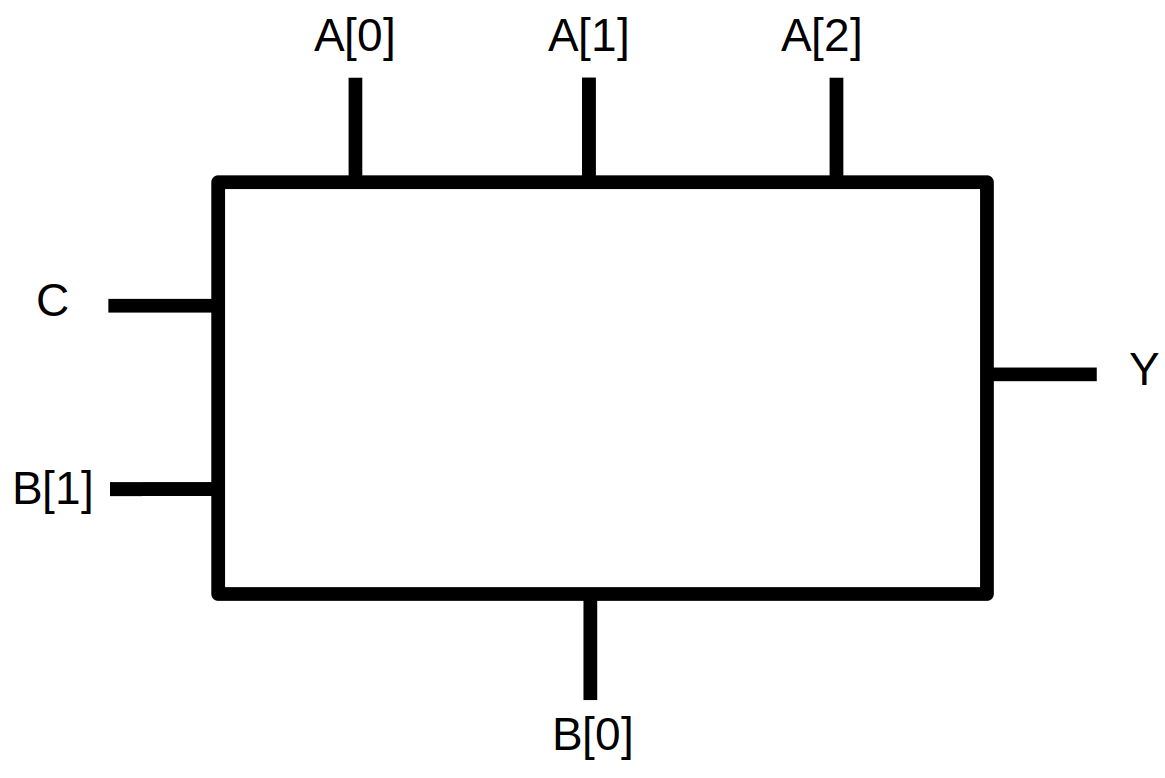

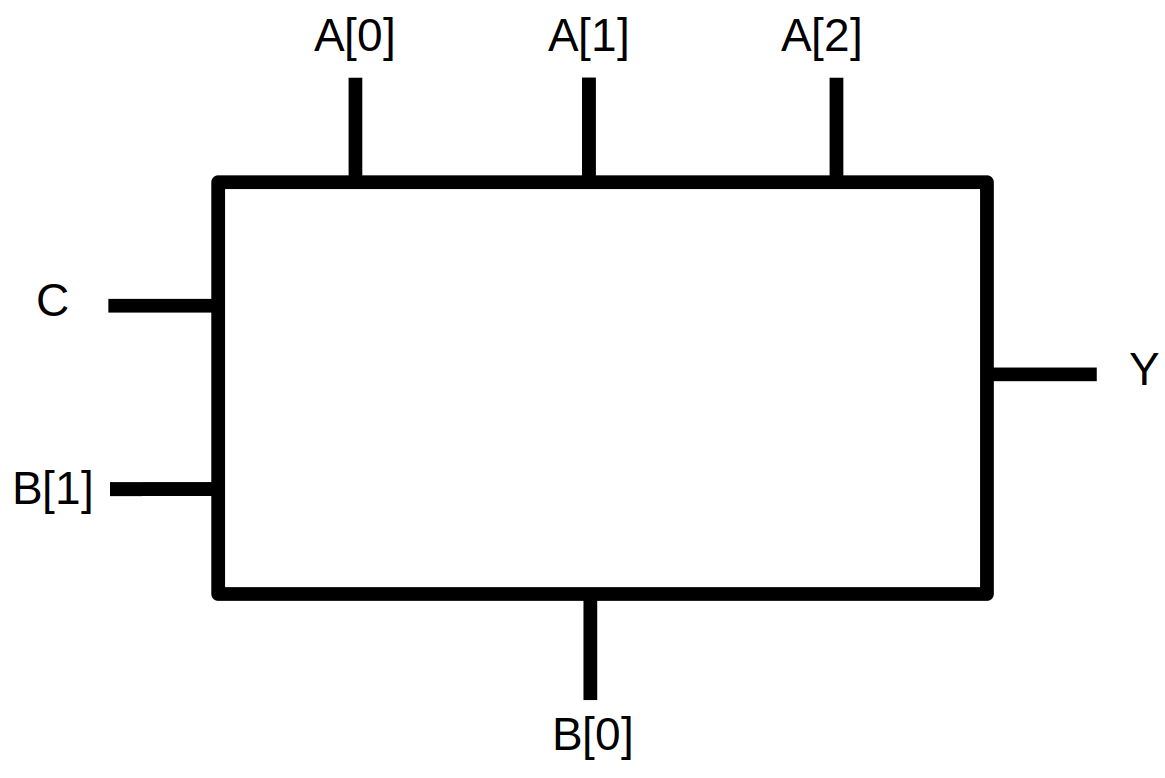

Por ejemplo, considere el ordenamiento mostrado para el layout de la siguiente figura.

Para lograr dicho acomodo, se deberá utilizar un archivo

pin_order.cfg como el siguiente:

#N

A\[0\]

A\[1\]

A\[2\]

#S

B\[0\]

#E

Y

#W

B\[1\]

C

Note que los paréntesis cuadrados son interpretados como caracteres especiales, por lo que se debe usar \ para poder usarlos como parte de los nombres de las señales.

Escriba el pin_order.cfg para implementar el ordenamiento que

usted sugirió y corra de nuevo el flujo de OpenLane. Utilice una etiqueta

distinta, para evitar que los resultados de esta corrida sobrescriban los

de el ordenamiento anterior. Abra el layout para verificar que el ordenamiento

deseado fue implementado. Haga zoom para que sea posible visualizar los

nombres de los puertos.

Realice además una comparación de los resultados de temporización de ambas implementaciones. Revise tanto los reportes de \textit{Total Negative Slack} (TNS) como \textit{Worst Negative Slack} (WNS). ¿Fueron efectivos sus cambios para mejorar el rendimiento?

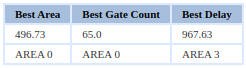

Revise el reporte de exploración del espacio de diseño de síntesis del

controlador USB realizado en el tutorial anterior. Determine las configuraciones

de síntesis que brindaron la mejor área y el mejor retardo. Por ejemplo,

en la figura la configuración AREA 0 brinda

la mejor área, mientras la configuración AREA 3 da el mejor retardo.

Ejecute el flujo de diseño de OpenLane para cada una de las dos

configuraciones de síntesis (mejor área y mejor retardo), para esto, modifique

la variable SYNTH_STRATEGY en el archivo config.json del

diseño usb. Modifique también la variable FP_CORE_UTIL

y asígnele un valor de 30.

Modifique también el archivo para que el período del reloj sea 4.0 en la configuración de menor retardo y 8.0 para la de menor área. Corra de nuevo los pasos para ejecutar OpenLane (utilice un tag diferente para no sobrescribir la corrida anterior). Utilice etiquetas distintas para cada configuración, para no sobrescribir los datos. Incluya un análisis completo que compare ambos resultados. En específico analice: